Instruction Set Manual Otfried Cheong 25/03/2007 · Does anyone know where I can find a table of AVR instructions listed by opcode? I'm trying to do some manual dissassembly of a hex dump here at work and Atmel's AVR Instruction set pdf lists the opcodes in binary throughout the text.

AVR Data Book 5. Instruction Set newit.gsu.by

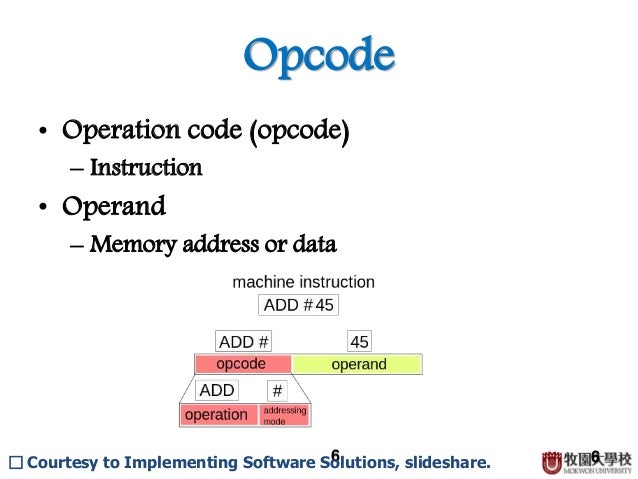

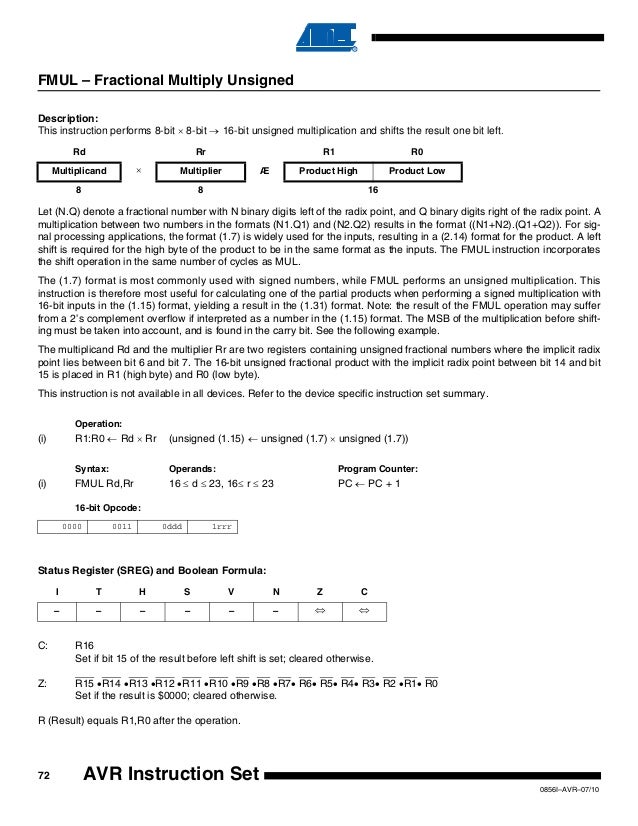

AVR Instruction Set blogspot.com. 11/10/2019 · opcode avr. avr instruction set wikipedia. avr rampz register. atmega8 assembler commands. Distinguish between immediate and implied addressing modes of 8086. 3: Pinouts of the Z80 processor (left) and the ATmega16 controller (right)., Operand & Opcode, in the context of assembly language, are part of an assembly instruction. I shall explain the concept with an example of AVR instruction. Image source: AVR Instruction Set Manual The above image describes the SBIW instruction. It....

4 Instruction Set Complete Instruction Set Summary Notes: 1. Not all instructions are available in all devices. Refer to the device specific instruction summary. 2. Cycle times for data memory accesses assume internal memory accesses, and are not valid for accesses via the external RAM interface. 25/03/2007 · Does anyone know where I can find a table of AVR instructions listed by opcode? I'm trying to do some manual dissassembly of a hex dump here at work and Atmel's AVR Instruction set pdf lists the opcodes in binary throughout the text.

68HC11 Instruction Set. Modified and corrected from Tom Dickens. Please notify me of any errors! Instruction set. Priscillya Cita. Download with Google Download with Facebook or download with email. Instruction set. Download. Instruction set. Priscillya Cita

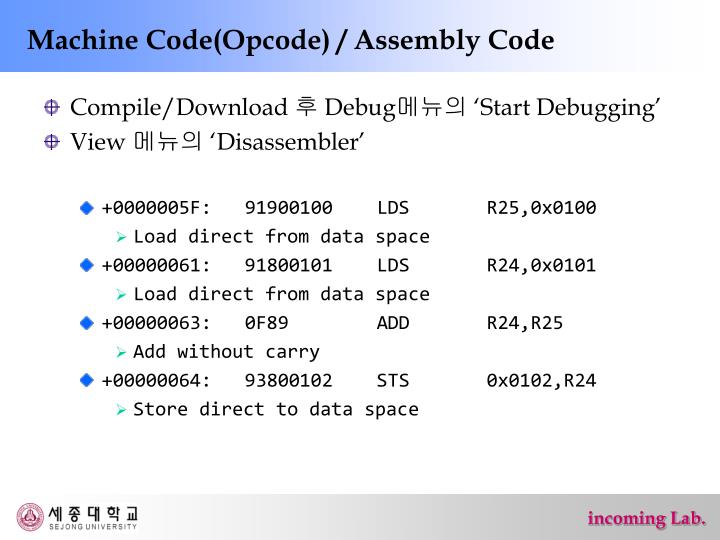

01/04/2019 · RJMP OPcode Help, Avr assembler. Ask Question 0. I have a question for solving the value of K in the opcode for rjmp. The opcode is 1100 kkkk kkkk kkkk. LEA instruction opcode generation. 1. Opcode and funct code in MIPs Assembly. 1. Assembly AVR ATMEGA128: CRC Algorithm. 0. 17/11/2004 · As you stated, the opcode is 0x9508 which is a 16-bit word with a high byte and a low byte. For a 'little endian' device, the low byte is stored first and then the high byte. For 'big endian' it is just the opposite. For opcodes, the avr is little endian. Here is a short test program I wrote:

27/04/1998 · VHDL implementation of 8-bit AVR processor. Contribute to sean9keenan/8_bit_avr development by creating an account on GitHub. The Atmel AVR instruction set is the machine language for the Atmel AVR, a modified Harvard architecture 8-bit RISC single chip microcontroller which was developed by Atmel in 1996. The AVR was one of the first microcontroller families to use on-chip flash memory for program storage.

11/10/2019 · opcode avr. avr instruction set wikipedia. avr rampz register. atmega8 assembler commands. Distinguish between immediate and implied addressing modes of 8086. 3: Pinouts of the Z80 processor (left) and the ATmega16 controller (right). Here is the instruction set list sorted by type, you can count once more : 35 official mnemonics. Microchip Datasheet DS33023A P.525. Now, we can try to re-arrange the table, and sort it by opcode number. I wrote the documented opcodes in green, and the undocumented opcodes in red :

Download >> Download Atmel microcontroller instruction set Read Online >> Read Online Atmel microcontroller instruction set ATMEL AVR 8 bit RISC MICROCONTROLLERS CPU design with a reduced instruction set as well as a simpler set of ATMEL MICROCONTROLLERS 8 bit RISC Author: Instruction Set Atmel 8051 Microcontrollers Hardware Manual 21/01/2018 · this one! this one also! (AVR Instruction Set with Instruction Templates.) My own style of finding opcode/instruction for ATmega: 1. Write an assembly line using AVR Studio 4 or Atmel Studio 7.0.

ldi r16, 0x20 out DDRB, r16 // set PB5 to output loop: out PINB, r16 // toggle PB5 ldi r17, 0xff wait: dec r17 brne wait rjmp loop translate to binary. The instruction encoding is defined in the AVR Instruction Set Manual and the register addresses you find in the register summary of the AVR’s datasheet. 11/10/2019 · opcode avr. avr instruction set wikipedia. avr rampz register. atmega8 assembler commands. Distinguish between immediate and implied addressing modes of 8086. 3: Pinouts of the Z80 processor (left) and the ATmega16 controller (right).

opcode The opcode is the machinecode representation of the instruction mnemonic. Several related instructions can have the same opcode. The opcode field is 6 bits long (bit 26 to bit 31). rs, rt, rd The numeric representations of the source registers and the destination register. Each midrange instruction is a 14-bit word divided into an OPCODE which specifies the instruc-tion type and one or more operands which further specify the operation of the instruction. The midrange Instruction Set Summary in Table 29-1 lists the instructions recognized by the MPASM

18/06/2014 · My idea is to program an atmega328 using the chips instruction set. For example in the past I have done something similar with the z80 processor where you can program the chip using its opcode to do simple functions such as add and subtract. The z80 development board had a keypad which was used to write the opcode and execute functions. Here is the instruction set list sorted by type, you can count once more : 35 official mnemonics. Microchip Datasheet DS33023A P.525. Now, we can try to re-arrange the table, and sort it by opcode number. I wrote the documented opcodes in green, and the undocumented opcodes in red :

ldi r16, 0x20 out DDRB, r16 // set PB5 to output loop: out PINB, r16 // toggle PB5 ldi r17, 0xff wait: dec r17 brne wait rjmp loop translate to binary. The instruction encoding is defined in the AVR Instruction Set Manual and the register addresses you find in the register summary of the AVR’s datasheet. ldi r16, 0x20 out DDRB, r16 // set PB5 to output loop: out PINB, r16 // toggle PB5 ldi r17, 0xff wait: dec r17 brne wait rjmp loop translate to binary. The instruction encoding is defined in the AVR Instruction Set Manual and the register addresses you find in the register summary of the AVR’s datasheet.

The Atmel AVR instruction set is the machine language for the Atmel AVR, a modified Harvard architecture 8-bit RISC single chip microcontroller which was developed by Atmel in 1996. The AVR was one of the first microcontroller families to use on-chip flash memory for program storage. 27/04/1998 · VHDL implementation of 8-bit AVR processor. Contribute to sean9keenan/8_bit_avr development by creating an account on GitHub.

Mysterious Opcodes in PIC16 Instruction Set. 25/11/2019 · Investigating the AVR / Arduino instruction set. Contribute to nlitsme/AVRInstructionSet development by creating an account on GitHub., 21/01/2018 · this one! this one also! (AVR Instruction Set with Instruction Templates.) My own style of finding opcode/instruction for ATmega: 1. Write an assembly line using AVR Studio 4 or Atmel Studio 7.0..

AVR Instruction Set hs-heilbronn.de

AVR instruction set selected opcode blocks. Instruction set. Priscillya Cita. Download with Google Download with Facebook or download with email. Instruction set. Download. Instruction set. Priscillya Cita, Avr Assembler Instruction Set I am trying to write some conditional jumps in AVR assembly using AVR-gcc. According to AVR instruction set manual, the brxx instructions take in an operand k..

Avr instruction set SlideShare

AVR Instruction Set blogspot.com. 25/11/2019 · Investigating the AVR / Arduino instruction set. Contribute to nlitsme/AVRInstructionSet development by creating an account on GitHub. https://ja.wikipedia.org/wiki/MIPS%E3%82%A2%E3%83%BC%E3%82%AD%E3%83%86%E3%82%AF%E3%83%81%E3%83%A3 Here is the instruction set list sorted by type, you can count once more : 35 official mnemonics. Microchip Datasheet DS33023A P.525. Now, we can try to re-arrange the table, and sort it by opcode number. I wrote the documented opcodes in green, and the undocumented opcodes in red :.

Download >> Download Atmel microcontroller instruction set Read Online >> Read Online Atmel microcontroller instruction set ATMEL AVR 8 bit RISC MICROCONTROLLERS CPU design with a reduced instruction set as well as a simpler set of ATMEL MICROCONTROLLERS 8 bit RISC Author: Instruction Set Atmel 8051 Microcontrollers Hardware Manual Type: Branch instruction Conditional relative branch. Tests the Zero flag (Z) and branches relatively to PC if Z is set. If the instruction is executed immediately after any of the instructions CP, CPI, SUB, or SUBI, the branch will occur if and only if the unsigned or signed binary number represented in Rd was equal to the unsigned or signed

MIPS Instruction Set Opcodes. MIPS Opcodes are divided into different categories. To understand each category you have to see the complete opcode list in table form then go through the description and example for each opcode. ldi r16, 0x20 out DDRB, r16 // set PB5 to output loop: out PINB, r16 // toggle PB5 ldi r17, 0xff wait: dec r17 brne wait rjmp loop translate to binary. The instruction encoding is defined in the AVR Instruction Set Manual and the register addresses you find in the register summary of the AVR’s datasheet.

25/03/2007 · Does anyone know where I can find a table of AVR instructions listed by opcode? I'm trying to do some manual dissassembly of a hex dump here at work and Atmel's AVR Instruction set pdf lists the opcodes in binary throughout the text. 4 Instruction Set Complete Instruction Set Summary Notes: 1. Not all instructions are available in all devices. Refer to the device specific instruction summary. 2. Cycle times for data memory accesses assume internal memory accesses, and are not valid for accesses via the external RAM interface.

68HC11 Instruction Set. Modified and corrected from Tom Dickens. Please notify me of any errors! Here is the instruction set list sorted by type, you can count once more : 35 official mnemonics. Microchip Datasheet DS33023A P.525. Now, we can try to re-arrange the table, and sort it by opcode number. I wrote the documented opcodes in green, and the undocumented opcodes in red :

68HC11 Instruction Set. Modified and corrected from Tom Dickens. Please notify me of any errors! 11/10/2019 · opcode avr. avr instruction set wikipedia. avr rampz register. atmega8 assembler commands. Distinguish between immediate and implied addressing modes of 8086. 3: Pinouts of the Z80 processor (left) and the ATmega16 controller (right).

opcode The opcode is the machinecode representation of the instruction mnemonic. Several related instructions can have the same opcode. The opcode field is 6 bits long (bit 26 to bit 31). rs, rt, rd The numeric representations of the source registers and the destination register. Operand & Opcode, in the context of assembly language, are part of an assembly instruction. I shall explain the concept with an example of AVR instruction. Image source: AVR Instruction Set Manual The above image describes the SBIW instruction. It...

21/01/2018 · this one! this one also! (AVR Instruction Set with Instruction Templates.) My own style of finding opcode/instruction for ATmega: 1. Write an assembly line using AVR Studio 4 or Atmel Studio 7.0. Each midrange instruction is a 14-bit word divided into an OPCODE which specifies the instruc-tion type and one or more operands which further specify the operation of the instruction. The midrange Instruction Set Summary in Table 29-1 lists the instructions recognized by the MPASM

18/06/2014 · My idea is to program an atmega328 using the chips instruction set. For example in the past I have done something similar with the z80 processor where you can program the chip using its opcode to do simple functions such as add and subtract. The z80 development board had a keypad which was used to write the opcode and execute functions. 27/04/1998 · VHDL implementation of 8-bit AVR processor. Contribute to sean9keenan/8_bit_avr development by creating an account on GitHub.

Instruction set. Priscillya Cita. Download with Google Download with Facebook or download with email. Instruction set. Download. Instruction set. Priscillya Cita 21/01/2018 · this one! this one also! (AVR Instruction Set with Instruction Templates.) My own style of finding opcode/instruction for ATmega: 1. Write an assembly line using AVR Studio 4 or Atmel Studio 7.0.

ldi r16, 0x20 out DDRB, r16 // set PB5 to output loop: out PINB, r16 // toggle PB5 ldi r17, 0xff wait: dec r17 brne wait rjmp loop translate to binary. The instruction encoding is defined in the AVR Instruction Set Manual and the register addresses you find in the register summary of the AVR’s datasheet. For detailed information on the AVR machine instruction set, as implements all the standard AVR opcodes. The following table summarizes the AVR opcodes, and else use next opcode entry 1001010010001000 clc 1001010011011000 clh 1001010011111000 cli 1001010010101000 cln 1001010011001000 cls 1001010011101000 clt

Page 1: Instruction Set Nomenclature AVR Microcontrollers AVR Instruction Set Manual OTHER Instruction Set Nomenclature Status Register (SREG) SREG Status Register Carry Flag Zero Flag Negative Flag Two’s complement overflow indicator N ⊕ V, for signed tests Half … 17/11/2004 · As you stated, the opcode is 0x9508 which is a 16-bit word with a high byte and a low byte. For a 'little endian' device, the low byte is stored first and then the high byte. For 'big endian' it is just the opposite. For opcodes, the avr is little endian. Here is a short test program I wrote:

AVR Instruction Set hs-heilbronn.de

(PDF) Instruction set Priscillya Cita Academia.edu. 4 Instruction Set Complete Instruction Set Summary Notes: 1. Not all instructions are available in all devices. Refer to the device specific instruction summary. 2. Cycle times for data memory accesses assume internal memory accesses, and are not valid for accesses via the external RAM interface., Issuu is a digital publishing platform that makes it simple to publish magazines, catalogs, newspapers, books, and more online. Easily share your publications and get them in front of Issuu’s millions of monthly readers. Title: Avr instruction set manual, Author: AaronBell3397, Name: Avr instruction set manual, Length: 3 pages, Page: 1.

Avr instruction set SlideShare

(PDF) Instruction set Priscillya Cita Academia.edu. 11/10/2019 · opcode avr. avr instruction set wikipedia. avr rampz register. atmega8 assembler commands. Distinguish between immediate and implied addressing modes of 8086. 3: Pinouts of the Z80 processor (left) and the ATmega16 controller (right)., 17/11/2004 · As you stated, the opcode is 0x9508 which is a 16-bit word with a high byte and a low byte. For a 'little endian' device, the low byte is stored first and then the high byte. For 'big endian' it is just the opposite. For opcodes, the avr is little endian. Here is a short test program I wrote:.

Operand & Opcode, in the context of assembly language, are part of an assembly instruction. I shall explain the concept with an example of AVR instruction. Image source: AVR Instruction Set Manual The above image describes the SBIW instruction. It... Download >> Download Atmel microcontroller instruction set Read Online >> Read Online Atmel microcontroller instruction set ATMEL AVR 8 bit RISC MICROCONTROLLERS CPU design with a reduced instruction set as well as a simpler set of ATMEL MICROCONTROLLERS 8 bit RISC Author: Instruction Set Atmel 8051 Microcontrollers Hardware Manual

01/04/2019 · RJMP OPcode Help, Avr assembler. Ask Question 0. I have a question for solving the value of K in the opcode for rjmp. The opcode is 1100 kkkk kkkk kkkk. LEA instruction opcode generation. 1. Opcode and funct code in MIPs Assembly. 1. Assembly AVR ATMEGA128: CRC Algorithm. 0. Type: Branch instruction Conditional relative branch. Tests the Zero flag (Z) and branches relatively to PC if Z is set. If the instruction is executed immediately after any of the instructions CP, CPI, SUB, or SUBI, the branch will occur if and only if the unsigned or signed binary number represented in Rd was equal to the unsigned or signed

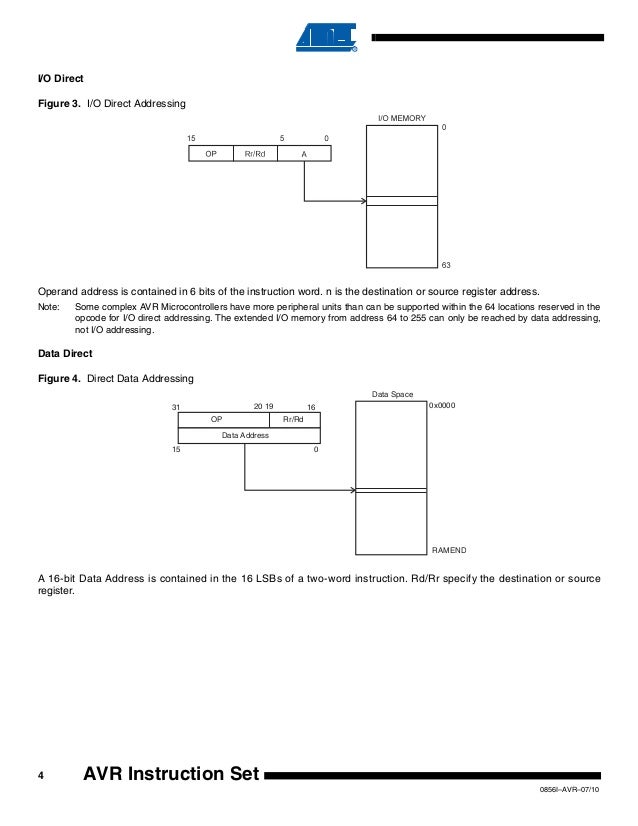

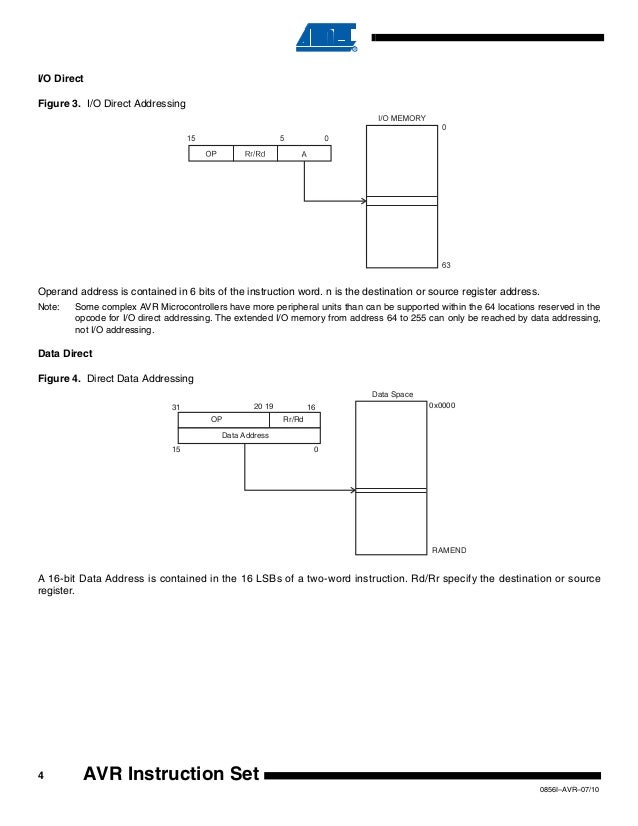

4 AVR Instruction Set 0856C–09/01 I/O Direct Figure 3. I/O Direct Addressing Operand address is contained in 6 bits of the instruction word. n is the destination or source register address. Note: Some complex AVR Microcontrollers have more peripheral units than can be supported within the 64 locations reserved in the opcode for I/O direct ldi r16, 0x20 out DDRB, r16 // set PB5 to output loop: out PINB, r16 // toggle PB5 ldi r17, 0xff wait: dec r17 brne wait rjmp loop translate to binary. The instruction encoding is defined in the AVR Instruction Set Manual and the register addresses you find in the register summary of the AVR’s datasheet.

25/04/2016 · How to create a 3D Terrain with Google Maps and height maps in Photoshop - 3D Map Generator Terrain - Duration: 20:32. Orange Box Ceo 8,218,500 views 11/10/2019 · opcode avr. avr instruction set wikipedia. avr rampz register. atmega8 assembler commands. Distinguish between immediate and implied addressing modes of 8086. 3: Pinouts of the Z80 processor (left) and the ATmega16 controller (right).

18/06/2014 · My idea is to program an atmega328 using the chips instruction set. For example in the past I have done something similar with the z80 processor where you can program the chip using its opcode to do simple functions such as add and subtract. The z80 development board had a keypad which was used to write the opcode and execute functions. 25/11/2019 · Investigating the AVR / Arduino instruction set. Contribute to nlitsme/AVRInstructionSet development by creating an account on GitHub.

Type: Branch instruction Conditional relative branch. Tests the Zero flag (Z) and branches relatively to PC if Z is set. If the instruction is executed immediately after any of the instructions CP, CPI, SUB, or SUBI, the branch will occur if and only if the unsigned or signed binary number represented in Rd was equal to the unsigned or signed 25/11/2019 · Investigating the AVR / Arduino instruction set. Contribute to nlitsme/AVRInstructionSet development by creating an account on GitHub.

Operand & Opcode, in the context of assembly language, are part of an assembly instruction. I shall explain the concept with an example of AVR instruction. Image source: AVR Instruction Set Manual The above image describes the SBIW instruction. It... 17/11/2004 · As you stated, the opcode is 0x9508 which is a 16-bit word with a high byte and a low byte. For a 'little endian' device, the low byte is stored first and then the high byte. For 'big endian' it is just the opposite. For opcodes, the avr is little endian. Here is a short test program I wrote:

4 AVR Instruction Set 0856G–AVR–07/08 I/O Direct Figure 3. I/O Direct Addressing Operand address is contained in 6 bits of the instructio n word. n is the destination or source register address. Download >> Download Atmel microcontroller instruction set Read Online >> Read Online Atmel microcontroller instruction set ATMEL AVR 8 bit RISC MICROCONTROLLERS CPU design with a reduced instruction set as well as a simpler set of ATMEL MICROCONTROLLERS 8 bit RISC Author: Instruction Set Atmel 8051 Microcontrollers Hardware Manual

4 AVR Instruction Set 0856G–AVR–07/08 I/O Direct Figure 3. I/O Direct Addressing Operand address is contained in 6 bits of the instructio n word. n is the destination or source register address. 4 AVR Instruction Set 0856G–AVR–07/08 I/O Direct Figure 3. I/O Direct Addressing Operand address is contained in 6 bits of the instructio n word. n is the destination or source register address.

Page 1: Instruction Set Nomenclature AVR Microcontrollers AVR Instruction Set Manual OTHER Instruction Set Nomenclature Status Register (SREG) SREG Status Register Carry Flag Zero Flag Negative Flag Two’s complement overflow indicator N ⊕ V, for signed tests Half … 4 AVR Instruction Set 0856G–AVR–07/08 I/O Direct Figure 3. I/O Direct Addressing Operand address is contained in 6 bits of the instructio n word. n is the destination or source register address.

AVR Data Book 5. Instruction Set newit.gsu.by

Avr instruction set SlideShare. 4 AVR Instruction Set 0856G–AVR–07/08 I/O Direct Figure 3. I/O Direct Addressing Operand address is contained in 6 bits of the instructio n word. n is the destination or source register address., 25/11/2019 · Investigating the AVR / Arduino instruction set. Contribute to nlitsme/AVRInstructionSet development by creating an account on GitHub..

Program ATmega328 Using Instruction Set. The instruction has no ModR/M byte; the offset of the operand is coded as a word or double word (depending on address size attribute) in the instruction. No base register, index register, or scaling factor can be applied (for example, MOV (A0–A3)). P: The reg field of the ModR/M byte selects a packed quadword MMX™ technology register. Q, 01/04/2019 · RJMP OPcode Help, Avr assembler. Ask Question 0. I have a question for solving the value of K in the opcode for rjmp. The opcode is 1100 kkkk kkkk kkkk. LEA instruction opcode generation. 1. Opcode and funct code in MIPs Assembly. 1. Assembly AVR ATMEGA128: CRC Algorithm. 0..

[Solved]AVR opcodes Arduino

Mysterious Opcodes in PIC16 Instruction Set. 4 AVR Instruction Set 0856G–AVR–07/08 I/O Direct Figure 3. I/O Direct Addressing Operand address is contained in 6 bits of the instructio n word. n is the destination or source register address. https://zh.wikipedia.org/zh-hk/MIPS%E6%9E%B6%E6%A7%8B 25/04/2016 · How to create a 3D Terrain with Google Maps and height maps in Photoshop - 3D Map Generator Terrain - Duration: 20:32. Orange Box Ceo 8,218,500 views.

The instruction has no ModR/M byte; the offset of the operand is coded as a word or double word (depending on address size attribute) in the instruction. No base register, index register, or scaling factor can be applied (for example, MOV (A0–A3)). P: The reg field of the ModR/M byte selects a packed quadword MMX™ technology register. Q 21/01/2018 · this one! this one also! (AVR Instruction Set with Instruction Templates.) My own style of finding opcode/instruction for ATmega: 1. Write an assembly line using AVR Studio 4 or Atmel Studio 7.0.

17/11/2004 · As you stated, the opcode is 0x9508 which is a 16-bit word with a high byte and a low byte. For a 'little endian' device, the low byte is stored first and then the high byte. For 'big endian' it is just the opposite. For opcodes, the avr is little endian. Here is a short test program I wrote: 17/11/2004 · As you stated, the opcode is 0x9508 which is a 16-bit word with a high byte and a low byte. For a 'little endian' device, the low byte is stored first and then the high byte. For 'big endian' it is just the opposite. For opcodes, the avr is little endian. Here is a short test program I wrote:

11/10/2019 · opcode avr. avr instruction set wikipedia. avr rampz register. atmega8 assembler commands. Distinguish between immediate and implied addressing modes of 8086. 3: Pinouts of the Z80 processor (left) and the ATmega16 controller (right). 25/03/2007 · Does anyone know where I can find a table of AVR instructions listed by opcode? I'm trying to do some manual dissassembly of a hex dump here at work and Atmel's AVR Instruction set pdf lists the opcodes in binary throughout the text.

27/04/1998 · VHDL implementation of 8-bit AVR processor. Contribute to sean9keenan/8_bit_avr development by creating an account on GitHub. 01/04/2019 · RJMP OPcode Help, Avr assembler. Ask Question 0. I have a question for solving the value of K in the opcode for rjmp. The opcode is 1100 kkkk kkkk kkkk. LEA instruction opcode generation. 1. Opcode and funct code in MIPs Assembly. 1. Assembly AVR ATMEGA128: CRC Algorithm. 0.

opcode The opcode is the machinecode representation of the instruction mnemonic. Several related instructions can have the same opcode. The opcode field is 6 bits long (bit 26 to bit 31). rs, rt, rd The numeric representations of the source registers and the destination register. 4 AVR Instruction Set 0856C–09/01 I/O Direct Figure 3. I/O Direct Addressing Operand address is contained in 6 bits of the instruction word. n is the destination or source register address. Note: Some complex AVR Microcontrollers have more peripheral units than can be supported within the 64 locations reserved in the opcode for I/O direct

Issuu is a digital publishing platform that makes it simple to publish magazines, catalogs, newspapers, books, and more online. Easily share your publications and get them in front of Issuu’s millions of monthly readers. Title: Avr instruction set manual, Author: AaronBell3397, Name: Avr instruction set manual, Length: 3 pages, Page: 1 Type: Branch instruction Conditional relative branch. Tests the Zero flag (Z) and branches relatively to PC if Z is set. If the instruction is executed immediately after any of the instructions CP, CPI, SUB, or SUBI, the branch will occur if and only if the unsigned or signed binary number represented in Rd was equal to the unsigned or signed

Download >> Download Atmel microcontroller instruction set Read Online >> Read Online Atmel microcontroller instruction set ATMEL AVR 8 bit RISC MICROCONTROLLERS CPU design with a reduced instruction set as well as a simpler set of ATMEL MICROCONTROLLERS 8 bit RISC Author: Instruction Set Atmel 8051 Microcontrollers Hardware Manual The Atmel AVR instruction set is the machine language for the Atmel AVR, a modified Harvard architecture 8-bit RISC single chip microcontroller which was developed by Atmel in 1996. The AVR was one of the first microcontroller families to use on-chip flash memory for program storage.

25/03/2007 · Does anyone know where I can find a table of AVR instructions listed by opcode? I'm trying to do some manual dissassembly of a hex dump here at work and Atmel's AVR Instruction set pdf lists the opcodes in binary throughout the text. Type: Branch instruction Conditional relative branch. Tests the Zero flag (Z) and branches relatively to PC if Z is set. If the instruction is executed immediately after any of the instructions CP, CPI, SUB, or SUBI, the branch will occur if and only if the unsigned or signed binary number represented in Rd was equal to the unsigned or signed

01/04/2019 · RJMP OPcode Help, Avr assembler. Ask Question 0. I have a question for solving the value of K in the opcode for rjmp. The opcode is 1100 kkkk kkkk kkkk. LEA instruction opcode generation. 1. Opcode and funct code in MIPs Assembly. 1. Assembly AVR ATMEGA128: CRC Algorithm. 0. opcode The opcode is the machinecode representation of the instruction mnemonic. Several related instructions can have the same opcode. The opcode field is 6 bits long (bit 26 to bit 31). rs, rt, rd The numeric representations of the source registers and the destination register.

The instruction has no ModR/M byte; the offset of the operand is coded as a word or double word (depending on address size attribute) in the instruction. No base register, index register, or scaling factor can be applied (for example, MOV (A0–A3)). P: The reg field of the ModR/M byte selects a packed quadword MMX™ technology register. Q 18/06/2014 · My idea is to program an atmega328 using the chips instruction set. For example in the past I have done something similar with the z80 processor where you can program the chip using its opcode to do simple functions such as add and subtract. The z80 development board had a keypad which was used to write the opcode and execute functions.

The Atmel AVR instruction set is the machine language for the Atmel AVR, a modified Harvard architecture 8-bit RISC single chip microcontroller which was developed by Atmel in 1996. The AVR was one of the first microcontroller families to use on-chip flash memory for program storage. 01/04/2019 · RJMP OPcode Help, Avr assembler. Ask Question 0. I have a question for solving the value of K in the opcode for rjmp. The opcode is 1100 kkkk kkkk kkkk. LEA instruction opcode generation. 1. Opcode and funct code in MIPs Assembly. 1. Assembly AVR ATMEGA128: CRC Algorithm. 0.